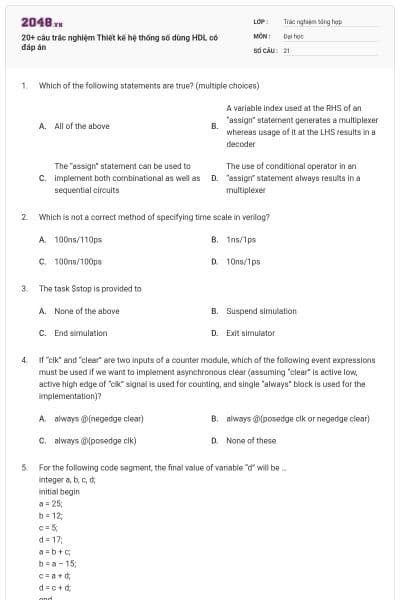

20+ câu trắc nghiệm Thiết kế hệ thống số dùng HDL có đáp án

21 câu hỏi

Which of the following statements are true? (multiple choices)

All of the above

A variable index used at the RHS of an “assign” statement generates a multiplexer whereas usage of it at the LHS results in a decoder

The “assign” statement can be used to implement both combinational as well as sequential circuits

The use of conditional operator in an “assign” statement always results in a multiplexer

Which is not a correct method of specifying time scale in verilog?

100ns/110ps

1ns/1ps

100ns/100ps

10ns/1ps

The task $stop is provided to

None of the above

Suspend simulation

End simulation

Exit simulator

If “clk” and “clear” are two inputs of a counter module, which of the following event expressions must be used if we want to implement asynchronous clear (assuming “clear” is active low, active high edge of “clk” signal is used for counting, and single “always” block is used for the implementation)?

always @(negedge clear)

always @(posedge clk or negedge clear)

always @(posedge clk)

None of these

For the following code segment, the final value of variable “d” will be …

integer a, b, c, d;

initial begin

a = 25;

b = 12;

c = 5;

d = 17;

a = b + c;

b = a – 15;

c = a + d;

d = c + d;

end

58

51

40

53

Which of the following is true for the following module?

module mydesign (a,b);

input [1:0] b;

output reg a;

always @(b)

begin

if (b==2'b00) a = 1'b0;

else if (b==2'b11) a = 1'b0;

else a = 1'b1;

end

end module

A latch will be generated for the output "a"

The synthesis tool will give an error

A combinational circuit implementing an AND function will be generated

A combinational circuit implementing a XOR function will be generated

Which of the following statements is/are true? (multiple choices)

The “assign” statement implements continuous assignment between the expression specified on the right-hand side and a “net” type variable specified on the left-hand side

The “assign” statement implements continuous assignment between the expression specified on the right-hand side and a “reg” type variable specified on the left-hand side

None of these

The “assign” statement can be used to model a latch, which is a sequential circuit

If A = 4b011 and B = 4b0011, then the result of A ** B will be

9

Invalid expression

6

27

The following code segment generates a periodic clock signal “clk” with time period:

initial clk = 1’b1;

always #10 clk = ~clk;

None of these

10

20

30

What does the following code segment indicate?

initial clk = 1’b0;

always #5 clk = ~clk;

Raising edges of the clock will appear at times 5, 15, 25, 35, …

Raising edges of the clock will appear at times 5, 10, 15, 20, …

None of the above

Raising edges of the clock will appear at times 10, 20, 30, 40, …

Which of the following is true for the module given below?

module mydesign (a,b,c);

input c;

output reg a, b;

always @(c)

begin

if (c == 1’b0)

begin

b <= ~a;

a <= ~(c | b);

end

else if (c == 1’b1)

a <= ~(b ^ c);

end

endmodule

(multiple choices)

The synthesis tool will give an error

A pure combinational circuit using NOT, NOR, and XNOR logic gates will be implemented

A latch with enable signal c will be generated for the output

A 2-to-1 multiplexer will be generated

Which of the following is true about the following code segment?

integer x, y;

initial

begin

x = 15;

y = 10;

end

initial

repeat (x) $display (“x=%d”, x);

initial

while (y < 12)

begin

y = y + 1;

x = x - 1;

end

It cannot be determined exactly how many times the value of ‘x’ will be printed

The simulation will print the current value of ‘x’ 15-times

The simulation will print the current value of ‘x’ 13-times

The simulation will always display 15 as the value of ‘x’

Consider the following Verilog module.

module guess (data, cond, result);

input [7:0] data;

input [1:0] cond;

output reg result;

always @(data)

begin

if (cond == 2’b00)

result = |data;

else

result = ~^data;

end

endmodule

Which of the following are true when the module is synthesized? (multiple choices)

The synthesize system will generate a wire for result

A combinational circuit will be generated

None of the above

A sequential circuit with a storage element for result will be generated

What will the following code segment generate on synthesis, assuming that the four variables data0, data1, data2 and data3 map into four latches/flip-flops?

always @(posedge clock)

begin

data3 = din;

data2 = data3;

data1 = data2;

data0 = data1;

end

None of these

A 4-bit parallel-in parallel-out register

A 4-bit shift register

Four D flip-flops all fed with the data “din”

What will the following code segment generate on synthesis, assuming that the four variables data0, data1, data2 and data3 map into four latches/flip-flops?

always @(posedge clock)

begin

data3 = din;

data2 = data3;

data1 = data2;

data0 = data1;

end

If A = 4b001x and B = 4b1011, then result of A + B will be

110x

1100

xxxx

None of the above

What will the following code segment do?

always @(posedge clock)

begin

y = x;

z = y;

x = z;

end

All the variables will get the value previously stored in “z”

Shift the values stored in the three variables

All the variables will get the value previously stored in “y”

All the variables will get the value previously stored in “x”

What does the construct “#5” indicate in simulation?

It specifies that the unit of delay is 5 nanoseconds

It pauses execution of the statements that follow after time 5

It schedules the execution of the next statement at time 5

It specifies a delay of 5 time units before executing the next statement

Which of the following is true for the “repeat” loop?

None of these

It can be used to iterate a block indefinitely

It can be used to repeat execution of the block exactly two times

It can be used to iterate a block until a specified condition is true

For the following Verilog code segment:

wire [7:0] A;

wire B;

assign B = ~|A;

If the value of A is 8’b00111001, what will be the value of {A[5:3], 3{B}}?

6’b111000

6’b011000

None of the above

6’b111111

If A, B, C and D are reg, reg, integer and wire variables respectively, each of size [7:0], which of the following is/are allowed inside a procedural block? (Multiple choice)

D = C + 1;

B[3:0] = D[4:1] + 1;

D = A + B;

C = A + D;

Consider the following Verilog code segment:

wire [5:0] A, B;

wire C;

assign C=^A;

If the values of A and B are 5’b10011 and 5’b01110 respectively, what will be the value of {A[3:1], 2{C}, B[2:0]}?

00100110

00111110

01111110

None of these